Striving for the advanced process market.

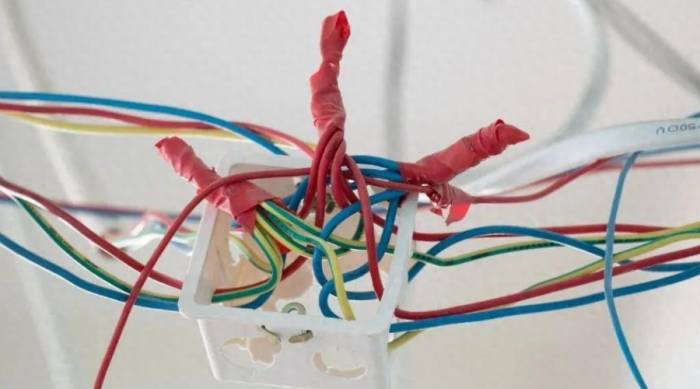

As Moore's Law progresses, transistors are becoming smaller, denser, and stacked in increasing numbers. It may require passing through 10 to 20 layers of stacks to provide power and data signals to the transistors below, leading to a more and more chaotic network where interconnects and power lines coexist. At the same time, as electrons are transmitted downward, the IR voltage drop phenomenon occurs, leading to power loss.

In addition to power loss, the space occupied by power supply lines is also a problem. The complex back-end process of chip power line wiring often occupies at least 20% of the resources. How to solve the problem of signal network and power supply network resource competition, and to make components miniaturized, has become the main challenge for chip designers. This has led to the semiconductor industry beginning to transfer the power supply network to the back of the chip.

TSMC's Super PowerRail technology debuts on the A16 process in 2025, increasing chip efficiency with technological complexity

The wafer foundry leader TSMC recently unveiled the A16 node process at a North American technology forum. In addition to accommodating more transistors and improving computational performance, it also reduces power consumption. Of particular concern, the A16 chip incorporates the Super PowerRail architecture and nanosheet transistors, driving the development of faster and more efficient data center processors. Notably, TSMC's A16 uses a different chip wiring method. The power lines that deliver electricity to the transistors will be located below the transistors instead of above, a technique known as backside power delivery, which is conducive to producing more efficient chips.

Advertisement

In fact, one of the best ways to optimize processors is to alleviate the IR voltage drop, a phenomenon that reduces the voltage received by chip transistors and degrades performance. The A16 wires are less prone to voltage drops, not only simplifying power distribution but also allowing for tighter packaging of chip circuits. The goal is to pack more transistors into the processor to enhance computational capabilities. Moreover, transistors consist of four main components: the source, drain, channel, and gate. The source is the entry point for current into the transistor, the drain is the exit, and the channel and gate are responsible for coordinating the movement of electrons in sequence.

TSMC has directly connected the power transmission lines to the source and drain in the A16 process technology. Regarding this, TSMC stated that the decision for a more complex design is because it helps to improve chip performance. In this case, the A16 using Super PowerRail will increase computational speed by 8% to 10% at the same Vdd (operating voltage) as N2P, or reduce power consumption by 15% to 20% at the same computational speed. The chip density is increased by up to 1.10 times, supporting data center products.Intel's PowerVia is set to be production-ready on Intel 20A by 2024

Similar to TSMC's backside power delivery, Intel has also introduced its backside power solution, PowerVia. According to the introduction, power lines that would typically occupy 20% of the space on a chip are saved by PowerVia's backside power delivery technology, which also implies that the interconnect layers can be more relaxed.

In this regard, the Intel team previously created a Blue Sky Creek test chip to demonstrate that the power lines and interconnects of the backside power delivery technology can be separated and have larger diameters, thereby improving power supply and signal transmission. Test results showed that the standard cell utilization rate in most areas of the chip exceeded 90%, the platform voltage was reduced by 30%, and a 6% frequency increase was achieved, while the cell density also increased significantly, with the potential to reduce costs. The PowerVia test chip also demonstrated good thermal properties, in line with the higher power density expected from logical scaling.

Additionally, PowerVia is also planned to be integrated into Intel's foundry services (IFS), enabling chips designed by customers to achieve faster improvements in product energy efficiency and performance. According to the official introduction of Intel's PowerVia backside power delivery technology, Intel will adopt the PowerVia backside power delivery technology and RibbonFET all-gate transistor architecture on the Intel 20A process technology, expected to be production-ready in the first half of 2024, for future mass production of the client ARL platform, with the wafer fab initiating the first stepping.

Samsung plans to apply it on the SF1.4 process starting in 2027

As for TSMC's other competitor, Samsung, in addition to being the first to transition to GAA transistor technology, its backside power delivery technology (BSPDN) is also a key weapon in Samsung's pursuit of advanced processes. According to previous reports from South Korean media, Samsung's foundry division's chief technologist, Jung Ki-tae, announced that the backside power delivery technology will be used for the 1.4-nanometer process in 2027.The report indicates that compared to traditional front-end power supply networks, Samsung's back-end power supply network has successfully reduced the consumption of wafer area by 14.8%. This allows the chip to have more space, which can accommodate more transistors, thereby enhancing overall performance. The wiring length is reduced by 9.2%, which helps to lower resistance and allow more current to pass through, reducing power consumption and improving power transmission conditions. A Samsung Electronics representative stated that the mass production timeline for semiconductors using back-end power supply technology may vary depending on the customer's schedule. Samsung is currently investigating customer demand for the application of back-end power supply technology.

Comment